MIT、RAMを減らしSSDとFPGAで補うビッグデータ処理サーバを発表。同等性能で費用と電力削減

MITの研究者グループが、高価なDRAMを減らしフラッシュメモリと独自のFPGAで補ったビックデータ処理用サーバアーキテクチャを発表しました。大量のデータを扱う典型的なタスクであれば、大量のDRAMを積んだサーバと同等の性能を実現しつつ、コストと消費電力の大幅な削減が可能になるとしています。

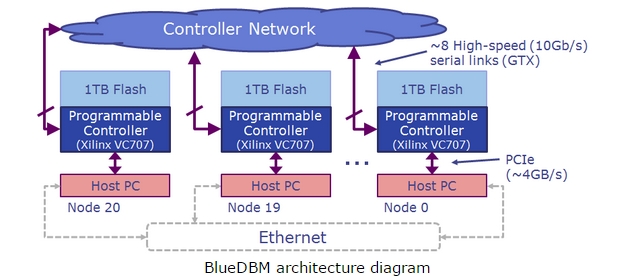

MITが発表したBlueDBMは、フラッシュメモリとFPGAを組み合わせたアプライアンス。各サーバからストレージとして利用されるだけでなく、BlueDBM間で独自のネットワークを構築してサーバ間のデータのやり取りを高速化し、ビックデータの分散処理における前処理をCPUではなくFPGAが担うことで処理を短縮します。

従来、サーバの処理速度を向上するためには、データを全てRAM上で処理することが必須という考え方が一般的でした。しかしビックデータの時代となりデータ量が膨大になりつつ昨今では、RAM容量を増やして対応するには非常にコストが嵩む問題があります。

BlueDBMを開発したのはMIT の Sang Woo Jun氏ら。大量のDRAMを積むかわりに低速なフラッシュメモリを使いつつ、RAMに近い性能を実現するための施策として研究が進められてきました。

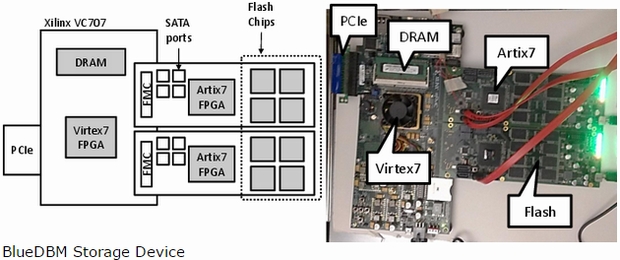

BlueDBMのプロトタイプの主な仕様は

- ホストとの接続 PCIe Gen1(2GB/s)、将来的には、PCIe GEN2(4GB/s)

- ノード間の接続 8倍速SATAリンク(10GB/s)

- ドータカード間のリンク シリアル通信(2.2GB/s)

- フラッシュコントローラ Artix7 FPGA(ドータカードに各1)

- フラッシュ容量 1TB(2枚のドータカード,各1.6GB/s)

BlueDBMのアーキテクチャダイアグラムからも分かるように、ホストサーバ間のネットワーク接続とは別に、FPGAを内蔵したアプライアンス間のController Network(実体はSATAケーブルによる接続)を構築できます。

MITの研究者は、Quanta、Samsung、Xilinxといったスポンサー企業の協力もあり、20台のサーバでプロトタイプを完成させました。RAMを大量に積まない場合のボトルネックをアプライアンスのノード間通信と、FPGAが行う事前処理などで補うことにより、イメージ検索やPageRankアルゴリズム、分散メモリキャッシュ memcachedなどのタスクでは、RAMを大量に積んだ場合と同等の性能を出すことができたとしています。

あくまで分散処理とデータ読み込みの高速化であってDRAMそのものの置き換え技術ではないと研究者が強調するとおり、事前処理はカスタマイズが必要になることや、扱うタスクを選ぶ特性はありますが、安価なフラッシュメモリで電力やコストを削減できる点、構成の拡張が比較的容易な点が大きな利点と言えそうです。

0 件のコメント :

コメントを投稿